为 iPhone 制造 Axx SoC 的台积电创始人刚刚宣布已准备好进行 5 纳米雕刻。该工艺将于 2020 年投入生产。从今年开始,台积电将采用改进的 7nm+ 雕刻工艺,这得益于 EUV 工艺,这有望降低高达 12% 的功耗,并提高 20% 数量级的密度。

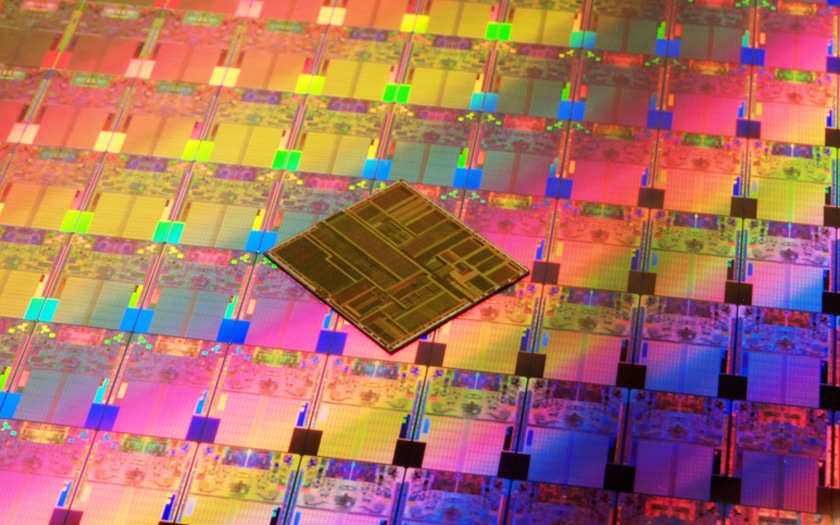

台积电是为最新一代 iPhone 生产 A10 Fusion、A11 Bionic 和 A12 Bionic SoC 的创始人,它已经是海思最早提供 7 纳米芯片的公司之一。创始人也有能力成为 5nm 雕刻工艺的先驱。在台积电新闻稿中宣布交付第一批“5nm [雕刻]工艺技术的基础设施”。这意味着目前该公司已经完成了文档(设计规则手册)、模型、工业设计套件、硅处理工艺和连接接口以及“全套 EDA 工具和设计流程”。

因此,首批 5nm SoC 将于 2020 年上市:“与台积电 7 纳米工艺相比,其创新的缩放功能可将 ARM Cortex-A72 内核的逻辑密度提高 1.8 倍,并实现 15% 的速度增益”,台积电解释道。 Apple Axx 芯片的制造商今年也将转向 7nm+ 工艺,这是一种通过 EUV 技术改进的 7nm 工艺,该工艺已经可以使密度显着增加 20% 左右,并且能耗降低高达 10%。为 12%。由于生产将于今年年初开始,我们有望在几个月内在苹果 A13 芯片中找到这种 7nm+ 制造工艺。

另请阅读:三星将从2019年开始生产7纳米处理器,与台积电竞争

台积电在这些新制造工艺方面的成功或失败预计将对行业产生影响。相当严格的创始人秩序保持着对行业的控制。台积电的客户是苹果,还有英伟达和AMD。这位创始人是否能够将硅的极限推向 5 纳米以上,还有待观察。这已经代表了极高的细节水平,其组件可以小至 1 纳米,或者只有 5 个硅原子宽。 5nm 雕刻之后是 3nm 雕刻,甚至更高。毫无疑问,这一技巧将涉及寻找硅的替代品。