全球最大的两家创始人台积电和三星已经在研发下一代 iPhone 和 Android 智能手机芯片。过渡到 3 nm,最终过渡到 2 nm。足以进一步显着降低组件的能耗,同时使其变得更加强大。

第一次让普通大众可以购买iPhone 12搭载5nm芯片。雕刻的精细度在移动行业至关重要,因为它允许在更小的空间中安装更多的晶体管,同时显着降低功耗。然而,苹果和许多品牌一样,没有自己的代工厂。

因此,我们呼吁该行业的领导者,尤其是几代人的台积电。新的A14仿生芯片嵌入了118亿个晶体管与 iPhone 11 的 A13 Bionic 芯片的 85 亿美元相比。当然我们可以反对,苹果在 5 nm 上并不孤单:华为刚刚推出了新的Mate 40和Mate 40 Pro,同样采用5纳米制程的全新麒麟9000芯片并且有更多的晶体管。但就华为而言,美国制裁使情况变得复杂。

只有少数创始人能够获得烧制 5 纳米及以上芯片的必要设备

台积电和竞争代工厂无法再向制造商供货自从在组件中美国新制裁生效。这些制裁禁止使用美国知识产权的公司向华为供应零部件未经商务部事先批准。台积电并未为华为获得授权。因此,在这家中国制造商订购的 1500 万颗麒麟 9000 芯片中,实际交付量只有800万。

这应该会严重限制华为中短期的销量。尤其是华为还没有计划仅在 Mate 40 上使用 Kirin 9000– 还体现在其 5G 网络解决方案和儿子 智能手机 柔韧 Mate X2。明年预计只有另一位参与者加入 5nm 俱乐部: 三星推出下一代 Exynos 芯片和Snapdragon 875,它应该为高通雕刻。或者,三星和台积电已与荷兰设备制造商 ASML 合作开发 3 纳米和 2 纳米雕刻技术。

有机会深入研究雕刻精细度的提高以及ASML 等设备制造商在提供更高效芯片方面发挥着核心作用。顺便说一句,自贸易战爆发以来,华为一直在寻找替代品,以避免高性能芯片供应消失。中国确实有国家级创始人中芯国际,但其刻蚀工艺仍然落后于竞争对手(14纳米,很快7纳米)。

当达到基本极限时,创新就会成倍增加

正是因为像ASML这样的设备制造商不再有权为这些玩家提供最先进的机器。雕刻的精细度降低得越多,我们就越能突破技术上的极限,尤其是当出现奇怪的效果时。因此,有必要采用更加复杂的尖端来保持恒定的雕刻精度,并避免电流泄漏的影响或在特定阈值后出现的干扰。。对于 5 nm,有必要开发极紫外 (EUV) 光刻工艺。

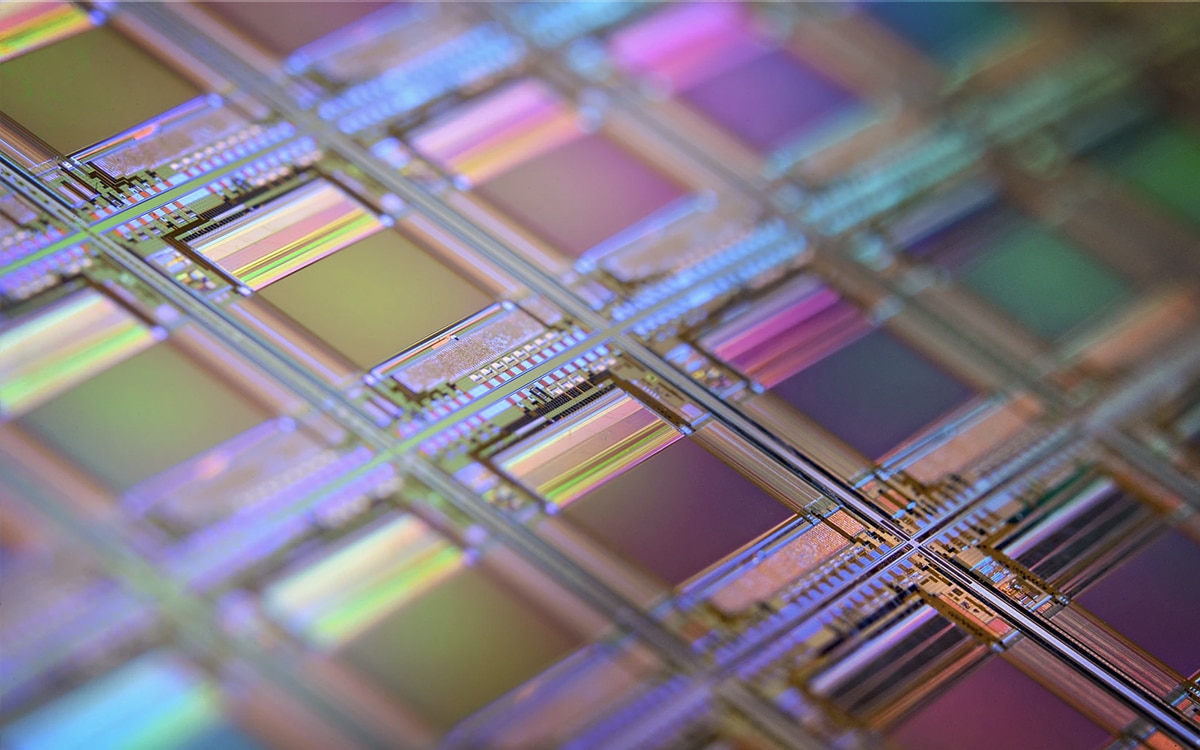

了解不同的层是用特别短的波长蚀刻在硅晶片上的。这晶体管栅极的设计也进行了调整以避免在这种规模上发生的量子效应(我们谈论的是只有几个原子宽的元素)。然而,为了提供更大的性能提升,台积电、ASML 和三星等其他代工厂也有兴趣增加每个芯片上的组件层数。

这些层使得创建更复杂的组件成为可能——这对于这些规模来说是至关重要的。同时使得芯片的设计更加复杂。所以现在,台积电目前采用 5nm 工艺,允许在同一组件上蚀刻多达 14 层。仅过渡到 3 nm 就可以带来在相同复杂度和晶体管数量的情况下,功率增加 15%,能耗降低 30%。

但毫无疑问可以做得更好:ASML 正在开发技术,使之成为可能在同一芯片上以 3 nm 烧录多达 20 层。这一进步将使智能手机 SoC 和 DRAM 内存芯片受益。对于 3 nm,台积电将选择所谓的 FinFET 晶体管设计:这些实际上是具有两个栅极的晶体管。 FinFET 这个名称来源于组件某些区域的形状,这些区域在芯片表面形成一种薄片。这使得可以增加频率,同时增加元件的密度。

为了过渡到 2 nm,台积电将进一步改变晶体管的设计,转而采用 GAAFET 技术(四周都是门)三星与 MBCFET 技术并行开发,超越 3 nm。随着我们越来越接近硅蚀刻的基本极限,我们应该在未来几年看到令人兴奋的创新。也许正在等待寻找替代方案。

来源 :电话竞技场